Completed

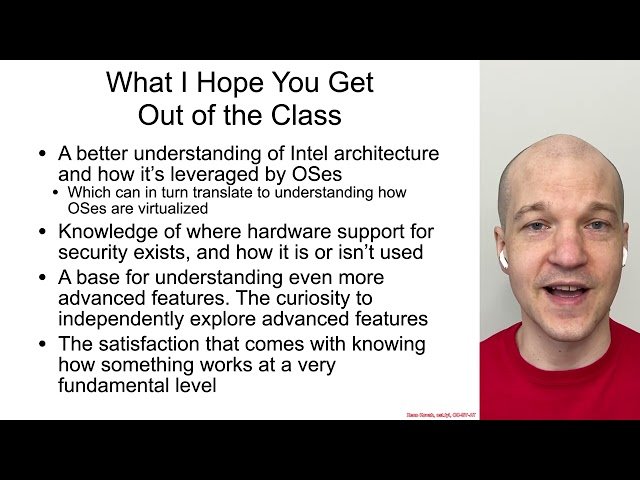

Class Intro - Architecture 2001: x86-64 OS Internals

Class Central Classrooms beta

YouTube videos curated by Class Central.

Classroom Contents

Architecture 2001 - Intel x86-64 OS Internals

Automatically move to the next video in the Classroom when playback concludes

- 1 Class Intro - Architecture 2001: x86-64 OS Internals

- 2 Warm Up: CPUID Instruction

- 3 Intel Processor Execution Modes

- 4 Model Specific Registers

- 5 Privilege Rings & Segmentation - Privilege Rings Start

- 6 Privilege Rings - Segmentation & Segment Registers 1

- 7 Privilege Rings - Segmentation & Segment Registers 2 - Labs: U_SegRegs & K_SegRegs

- 8 Privilege Rings - Segmentation & Segment Registers 3 - Optional: 32-bit Throwback

- 9 Global Descriptor Table (GDT) & Local Descriptor Table (LDT) 1 - Global Descriptor Table Register

- 10 Global Descriptor Table (GDT) & Local Descriptor Table (LDT) 2 - Lab: Look at the GDTR

- 11 Global Descriptor Table (GDT) & Local Descriptor Table (LDT) 3 - Local Descriptor Table Register

- 12 Global Descriptor Table (GDT) & Local Descriptor Table (LDT) 4 - Lab: Look at the LDTR

- 13 Global Descriptor Table (GDT) & Local Descriptor Table (LDT) 5 - GDTR & LDTR: What Did We Learn?

- 14 Privilege Rings - Segment Descriptors 1 - Segment Descriptors

- 15 Privilege Rings - Segment Descriptors 2 - Lab: Hand-parsing GDT Segment Descriptors & Using SwishDbg

- 16 Privilege Rings - Segment Descriptors 3 - What Did We Learn?

- 17 Privilege Rings & Segmentation - Privilege Rings End

- 18 Privilege Rings & Segmentation - Call Gates

- 19 Privilege Rings & Segmentation - A Return To Read(ing) The Fun Manual!

- 20 Privilege Rings & Segmentation - Implicit and Explicit Use of Segmentation

- 21 Privilege Rings & Segmentation - Conclusion

- 22 Interrupts - Interrupts vs. Exceptions

- 23 Interrupts - Software Interrupt Instructions

- 24 Interrupts - Tasks and the Task State Segment (TSS)

- 25 Interrupts - Tasks and the Task State Segment (TSS) - Lab: Examine a 64-bit TSS

- 26 Interrupts - Interrupt Descriptor Table (IDT)

- 27 Interrupts - Interrupt Descriptors

- 28 Interrupts - Interrupt Descriptors - Labs: Pearly Interrupt Gates 1 & 2

- 29 Interrupts - Interrupt Descriptors - What Did We Learn?

- 30 Interrupts - Interrupt Masking

- 31 Interrupts - Red Pill and Virtualization Detection

- 32 Interrupts - Conclusion

- 33 System Calls - System Calls Design Background

- 34 System Calls - syscall vs sysenter 32-bit vs. 64-bit Instruction Compatibility

- 35 System Calls - syscall/sysret: x86-64's Preferred System Call Instructions

- 36 System Calls - Visualizing the syscall MSR Usage

- 37 System Calls - Lab: Syscall MSR Investigation

- 38 System Calls - Optional: sysenter/sysexit: x86-32's preferred system call instructions

- 39 System Calls - Syscall-adjacent Tech (swapgs, {rd,wr}{fs,gs}base)

- 40 System Calls - Conclusion

- 41 Read the TimeStamp Counter (RDTSC) Assembly Instruction

- 42 Read the TimeStamp Counter (RDTSC) - Labs: U_Guestimate & U_NavelGaze

- 43 Paging - Paging Introduction

- 44 Paging - Paging and the Control Registers

- 45 Paging - Paging and the Control Registers - Lab: Read the Control Registers

- 46 Paging - Paging and the Control Registers - What Did We Learn?

- 47 Paging - Page Tables - MAXPHYADDR

- 48 Paging - Page Tables - 32 bit Linear to 32 bit Physical, 4KB Pages

- 49 Paging - Page Tables - 32 bit Linear to 32 bit Physical, 4MB Pages

- 50 Paging - Page Tables - 32 bit Linear to 40 bit Physical, Physical Address Extensions (PAE)

- 51 Paging - Page Tables - 48 bit Linear to 52 bit Physical, 4-level Paging, 4KB, 2MB, 1GB Pages

- 52 Paging - Page Tables - (Optional) 57 bit Linear to 52 bit Physical, 5-level Paging

- 53 Paging - Page Table Entries - CR3

- 54 Paging - Page Table Entries - CR3 - Lab: Page Table Walkabout 1

- 55 Paging - Page Table Entries - PML4E

- 56 Paging - Page Table Entries - PML4E - Lab: Page Table Walkabout 2

- 57 Paging - Page Table Entries - PML4E - Lab Example: Page Table Walkabout 2

- 58 Paging - Page Table Entries - Exploit Mitigation Aside: XD, SMEP, SMAP

- 59 Paging - Page Table Entries - PDPTE

- 60 Paging - Page Table Entries - PDPTE - Lab: Page Table Walkabout 3

- 61 Paging - Page Table Entries - PDPTE - Lab Example: Page Table Walkabout 3

- 62 Paging - Page Table Entries - PDE

- 63 Paging - Page Table Entries - PDE - Lab: Page Table Walkabout 4

- 64 Paging - Page Table Entries - PDE - Lab Example: Page Table Walkabout 4

- 65 Paging - Page Table Entries - PTE

- 66 Paging - Page Table Entries - PTE - Lab: Page Table Walkabout 5

- 67 Paging - Page Table Entries - PTE - Lab Example: Page Table Walkabout 5

- 68 Paging - Canonical Addresses

- 69 Paging - Page Faults

- 70 Paging - Page Faults - Lab: Seeing What the Page Fault Handler Sees

- 71 Paging - Page Faults - Misc Points

- 72 Paging - Translation Lookaside Buffer (TLB)

- 73 Paging - Translation Lookaside Buffer (TLB) - Shadow Walker Rootkit

- 74 Paging - Non-executable Memory (NX/XD bit)

- 75 Paging - Non-executable Memory (NX/XD bit) - Lab: Checking the kernel's stack execute permissions

- 76 Paging - Non-executable Memory - Lab2: Checking a userspace process' stack execute permissions

- 77 Paging - Conclusion

- 78 Debugging - Software breakpoints

- 79 Debugging - Hardware Breakpoints - Hardware Debug Registers

- 80 Debugging - Hardware Breakpoints - Lab: Checking Debug Registers

- 81 Debugging - Hardware Breakpoints - Lab Walkthrough: Checking Debug Registers in WinDbg

- 82 Debugging - Hardware Breakpoints - Resume Flag (RF)

- 83 Debugging - Hardware Breakpoints - Trap Flag (TF) and Single-Stepping

- 84 Port I/O - Port I/O

- 85 Port I/O - Lab: K_VMWare_PortIO

- 86 Port I/O - CMOS Background

- 87 Port I/O - Lab: K_CMOS_PortIO

- 88 Conclusion - Architecture 2001: x86-64 OS Internals